1. 引言

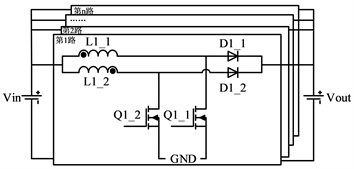

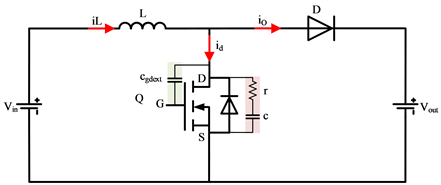

如图1所示,交错并联Boost变换器作为一种非隔离大功率的DC/DC变换器,因具有输入电流纹波低、电压增益高等优点,被广泛应用于氢燃料电池车的功率转换。Boost变换器作为氢燃料电池车驱动系统的主要部件,受汽车车身空间限制,对其功率密度要求较高。相比于传统的Si MOSFET,SiC MOSFET因具有耐压水平高、温度稳定性好、工作频率高等特性,可以极大减小变换器主回路中电感、电容元件的体积,使变换器的功率密度得到成倍数的提高 [1] 。

Figure 1. Topology diagram of interleaved parallel Boost converter

图1. 交错并联Boost变换器拓扑图

将SiC MOSFET引入到交错并联Boost变换器中,在提高开关频率和运行效率的同时,还减小了变换器的体积和损耗,但SiC MOSFET极间寄生电容较小,开关速度快,导致其对电路中杂散电感十分敏感,在关断过程中会产生很大的di/dt。同时,SiC MOSFET作为单极型器件,在关断过程中不具有拖尾电流效应,极易产生较大的瞬时电压尖峰 [2] 。

为抑制SiC MOSFET关断时的电压尖峰,文献 [3] 提出一种电流注入型有源驱动电路,通过控制输入到栅极电流的大小来抑制电压尖峰,该方法在牺牲较少损耗的情况下能够有效抑制电压尖峰,但控制较为复杂、实现难度大;增加栅极电阻能够明显减小SiC MOSFET的尖峰和振荡,但是增大驱动电阻会增加开关损耗和驱动损耗 [4] 。

本文针对SiC MOSFET在关断时,电压尖峰产生的机理进行理论分析后,分别从减小SiC MOSFET关断时的电流;降低SiC MOSFET的关断速度,提出了两种电压尖峰的抑制方法,并通过试验验证了所提方法的有效性。

2. 关断电压尖峰的机理分析

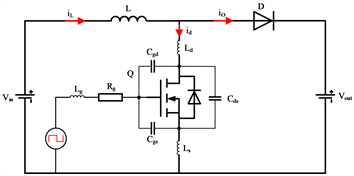

在交错并联Boost变换器中,各相拓扑结构相同,只是开关管Q的导通时序不同,因此本文只对其中一相进行分析。为详细分析SiC MOSFET关断时,电压尖峰和振荡的形成机理,本文搭建了图2所示的Boost电路。其中,Vin为直流母线输入电压,Vout为直流母线输出电压,L为储能电感,Rg为驱动电阻,Q为SiC MOSFET,D为SiC Diode;电路中的主要寄生参数包括:SiC MOSFET的栅源极间电容Cgs、漏源极间电容Cds、栅漏极间电容Cgd、源极线路上的杂散电感Ls和漏极线路上的杂散电感Ld,驱动回路杂散电感Lg。

Figure 2. Topology diagram of Boost topology

图2. Boost电路拓扑图

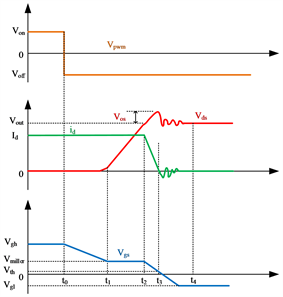

根据电压和电流的状态,SiC MOSFET的关断过程分为4个阶段 [5] ,如图3所示。

Figure 3. Shutdown process diagram of SiC MOSFET

图3. SiC MOSFET的关断过程图

2.1. 关断延时阶段(t0~t1)

在t0时刻,驱动信号Vpwm由高电平变为低电平,输入电容Ciss (Ciss = Cgs + Cgd)通过栅极驱动电阻Rg、栅极杂散电感Lg和漏极杂散电感Ls进行放电。在该阶段,漏极电流id为恒定值,栅源极电压Vgs逐渐下降至米勒电压Vmiller,对回路列写KVL方程,可得:

(1)

其中,Vgl是驱动电压的低电平,栅极电流ig由式(2)计算得到。

(2)

2.2. 关断延时阶段(t1~t2)

在此阶段内,SiC MOSFET的栅源极电压Vgs和漏极电流id保持不变,Vds快速上升,直至达到Vout。在此阶段,SiC MOSFET完成线性区到饱和区的过渡。电压的变化率dvds/dt可由公式(3)计算得到。

(3)

2.3. 电流下降阶段(t2~t3)

在该阶段,漏极电流id开始下降,二极管D正向导通,负载电流从开关管Q向二极管D转移。栅源极电压Vgs继续下降,直至达到阈值电压Vth,SiC MOSFET关断,漏极电流id降为0。

根据开关管Q的传输特性,该阶段漏极电流id的变化率为:

(4)

其中,gm是SiC MOSFET的跨导。

由式(1)、(2)和(4)可得,漏极电流id的变化率和驱动电压Vgl的关系式为:

(5)

此阶段,由于漏极电流id的快速变化,会在电路的杂散电感上产生压降,这部分电压叠加到SiC MOSFET的D、S之间,就会产生较大的电压尖峰。由于di/dt较高,寄生电感将产生较大的压降,从而导致设备Vos的电压过高。忽略二极管D的导压降,根据KVL可得:

(6)

其中,Lp是回路中杂散电感的总和。

(7)

2.4. 电流下降阶段(t3~t4)

在此阶段,栅源极电压Vgs继续下降至Vgl,SiC MOSFET完全关断。Vds因主回路中的阻尼形成衰减振荡,如式(8)所示。变化的漏源电压Vds作用在输出电容Coss上,漏极电流id在下降到零后同样会形成衰减振荡,如式(9)所示。

(8)

(9)

其中,α、ω、Coss的求解式分别为:

(10)

(11)

(12)

通过对关断过程的分析可知,电压尖峰发生在电流下降阶段,主要由该阶段的高di/dt引起。此外,电压尖峰过高也与关断速度dV/dt有关。因此,在抑制电压尖峰时可从这几个方面考虑:减小线路中的杂散电感;减小SiC MOSFET关断前的电流;降低SiC MOSFET的关断速度。

3. 电压尖峰抑制方法

3.1. 减小SiC MOSFET关断时的电流

在工程应用中,减小SiC MOSFET关断时电流的方法有很多,如增加RC吸收电路、RCD吸收电路、箝位式RCD吸收电路 [6] 。在这几种吸收电路中,RC吸收电路器件数量较少、体积较小,基本不会影响PCB板布局的紧凑性,同时与其它吸收电路相比产生的额外损耗也不会很大,因此RC吸收电路常用于减小SiC MOSFET关断时的电流。

Figure 4. Boost converter with added RC absorption circuit

图4. 增加RC吸收电路后的Boost变换器图

如图4所示为增加RC吸收电路后的Boost变换器图,在开关管Q关断时,缓冲电容C吸收额外电荷,减缓电压上升速度;在开关管Q关断后,缓冲电容C可阻断寄生参数形成的谐振回路,抑制电压和电流的振荡。开关管Q导通时,缓冲电容C吸收的能量通过缓冲电阻R与开关管Q形成放电回路。缓冲电阻的使用,虽然减缓了开关管Q关断时电容C吸收电荷的速度,但在开关管Q导通时,能够增大开关器件的电流应力。因此在工程应用过程中,要根据实际工况对R和C的取值进行权衡 [7] 。

3.2. 降低SiC MOSFET的关断速度

在应用中,将开关管Q开关过程中的dV/dt控制在一定的限值是非常重要的,特别是对于开关速度快的SiC器件,可将电压尖峰控制在合理范围内。由公式(13)中各参数间的关系可知,增大Rg和Cgd都能够降低dV/dt [8] 。其中,对于Si MOSFET和IGBT,增大驱动电阻Rg的阻值是降低dV/dt最常用的方法,但对于SiC MOSFET,其对线路中的杂散电感较为敏感。当线路中杂散电感较大时,通过适当的增加栅极电阻的值,无法将dV/dt控制在合适的范围,若通过进一步增大Rg的值降低dV/dt,Rg较大的阻值会带来额外的损耗,降低系统效率。

(13)

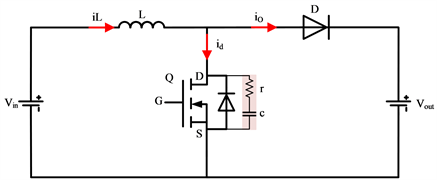

通过实际应用发现,如图5在SiC MOSFET的栅极和漏极之间并接外部电容Cgdext的方式,增大Cgd的值可有效降低SiC MOSFET的开关速度,同时不会产生过多的损耗。

Figure 5. Boost converter with c connected in parallel between DG

图5. DG间并接Cgdext后的Boost变换器图

4. 试验验证及分析

4.1. RC吸收电路的效果验证

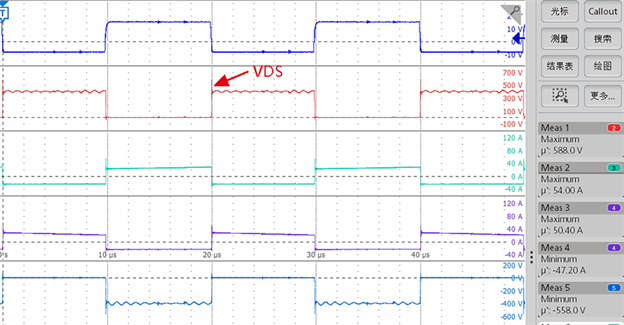

按照表1所示的试验参数,在输入电压200 V,输出电压400 V,输入电流300 A的工况下,分别对SiC MOSFET的DS两端无RC吸收和并联RC吸收对电压尖峰的抑制效果进行验证。

图6为SiC MOSFET的DS两端未并接RC吸收电路的试验结果,由试验结果可知此时VDS的尖峰电压为588 V;图7为SiC MOSFET的DS两端并接RC (R = 5 Ω、C = 1 nF)吸收电路的试验结果,从由试验结果可知此时VDS的尖峰电压为498 V。由试验结果对比可知,RC吸收电路能够很好的降低电压尖峰。

Figure 6. Waveform without RC absorption at both ends of DS

图6. DS两端未并接RC吸收的波形图

Figure 7. Waveform with RC absorption at both ends of DS

图7. DS两端并接RC吸收的波形图

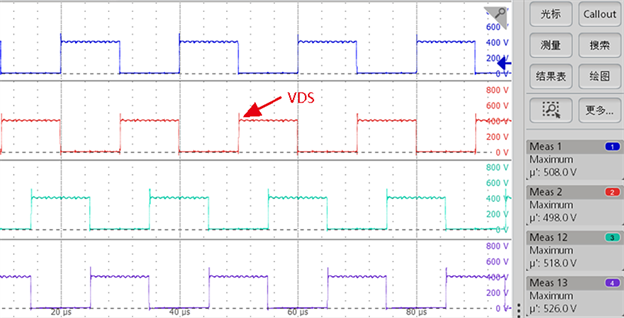

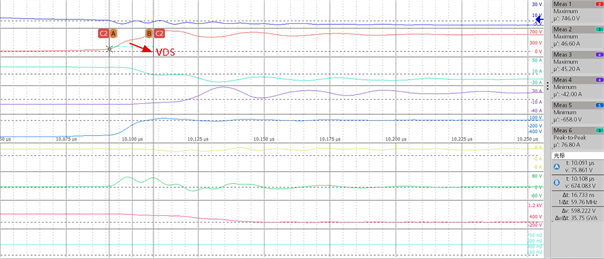

4.2. 增大Cgd的效果验证

在SiC MOSFET的DS两端并接RC吸收电路的基础上,将输出电压增大到600 V,发生SiC MOSFET击穿。针对该工况存在的问题,通过截取图8所示的SiC MOSFET关断时的细节波形,发现dV/dt的值为35.75 V/ns,经分析后确认为dV/dt过大导致。因此,在dV/dt过大时,单纯在DS两端并接RC吸收电路无法将SiC MOSFET的关断尖峰控制在安全范围内。

Figure 8. The detailed waveform of the turn-off of the non parallel capacitor between the DG of SiC MOSFET

图8. SiC MOSFET的DG间未并接电容关断时的细节波形图

为降低SiC MOSFET关断时的dV/dt,在DG间并接68 pF容值的电容,由图9中的试验结果可知,此时dV/dt的值为18.75 V/ns,与图8中的测试结果相比,dV/dt的值有了明显降低,且尖峰电压VDS也由746 V降为704 V。

Figure 9. The detailed waveform of the turn-off of the parallel capacitor between the DG of SiC MOSFET

图9. SiC MOSFET的DG间并接电容关断时的细节波形图

通过上述试验验证发现,在dV/dt较小时在SiC MOSFET的DS间并接RC吸收电路,能够有效降低DS间的电压尖峰,若dV/dt过大时,单纯通过调节RC吸收电路的参数无法有效降低DS间的电压尖峰。此时,就要先采用在DG间并接电容的方法,将dV/dt控制在合适的范围,然后再调节RC参数。

5. 结论

本文针对SiC MOSFET关断过程中出现的电压尖峰和振荡问题,对SiC MOSFET关断时电压尖峰和振荡的产生机理进行了分析,给出了影响电压尖峰和振荡的三种主要因素。针对这些主要因素,分别提出了相应的抑制方法,最后通过搭建仿真模型和试验平台,验证了所提方法对抑制电压尖峰和振荡的有效性。

参考文献