1. 引言

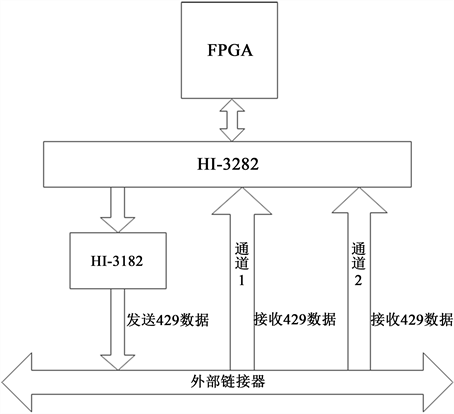

ARINC429是一种标准的高速差分信号通信总线,在民用和军用航空领域被广泛应用 [1]。例如波音727、737、747、757和767飞机,空客A310/A320、A330/A340飞机等。目前ARINC429总线接口一般都采用专用进口芯片 [2],配合ARINC429数据收发芯片(如HI-3282)和ARINC429数据发送驱动芯片(如HI-3182),形成2个数据接收通道和1个数据发送通道 [3]。这些专用进口芯片价格昂贵,且通道有限,使用非常不灵活。根据ARINC429总线协议,结合目前存在的问题,我们在FPGA中通过设计模块化、可配置的ARINC429总线协议,灵活扩展ARINC429通信通道,降低研发成本,并在FPGA外围配合ARINC429驱动芯片,可广泛应用于各种使用ARINC429总线的航空电子、航天电子、汽车电子以及工业控制等场合 [4]。

2. 协议设计

2.1. ARINC429协议简介

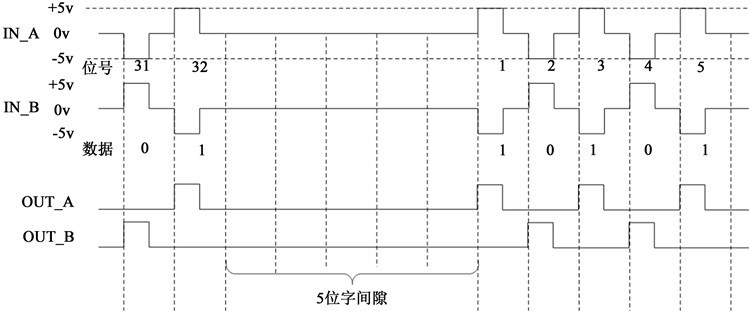

ARINC429总线传输的是双极性归零码信号 [5],数据信号是一对差分信号格式 [6],由专用驱动芯片驱动到总线进行电平转换,转换后的TTL电平才能与FPGA进行接口 [7],对应转换后的TTL电平如图1所示的OUT_A、OUT_B,其中连续传输的字与字之间至少有4个位的时间间隔,以便于发送下一组数据。

Figure 1. ARINC429 level conversion diagram

图1. ARINC429电平转换示意图

本文中基于FPGA的ARINC429协议设计包含发送部分与接收部分,两者均可通过对逻辑可重用模块寄存器的配置,实现发送与接收协议的独立工作,完成高速、低速两档的位速率设置、奇偶校验、中断控制等功能的配置。

2.2. ARINC429发送协议逻辑设计

发送部分主要是将总线上的信号转换成TTL电平差分串行码的转换 [8]。根据ARINC429协议,每一位数据前半个周期为TTL的具体值,后半个周期同时输出为0 [9]。其中,发送部分由总线接口、异步FIFO设计、奇偶校验、寄存器控制、并串转换等模块组成。发送协议的Verilog设计经过Vivado综合后的RTL模块原理图如图2所示。

Figure 2. Schematic diagram of ARINC429 sending protocol RTL module

图2. ARINC429发送协议RTL模块原理图

发送部分的工作过程:通过LBE总线将tx0_word[15:0]和tx1_word[15:0]锁存至寄存器fifo_wdata_latch[31:0]并形成FIFO的输入数据信号txfifo_in[31:0],在写时钟txfifo_wr_clk下,控制写使能txfifo_wr_en有效,将数据写入FIFO中缓存,直到满信号txfifo_full信号告警,便不再写入数据。通过在读时钟txfifo_rd_clk下,控制读使能txfifo_rd_en有效、发送使能信号tx_en有效,输出FIFO中缓存的单bit数据dout,直到空信号txfifo_empty告警,便不再继续输出数据。默认设置端口物理交换信号tx_line_sw为1’b1,当dout输出为1,tx0_out和tx1_out的前半周期为数据位,分别输出1和0,后半周期同时输出为0;dout输出为0时,tx0_out和tx1_out的前半周期分别输出0和1,后半周期同时输出为0。每次tx0_out、tx1_out输出之后,会有一个dout_ack输出响应有效信号。每个arinc429字由32位构成,格式如下表1所示。在32位数据传输过程中,遵循以下传输协议:先发送第1位,然后依次发送至32位,先传标号位,后传数据。当传输数据时,先传输最低位,但标号位应先传最高位,后传最低位。

Table 1. ARINC429 word format composition

表1. ARINC429字格式构成

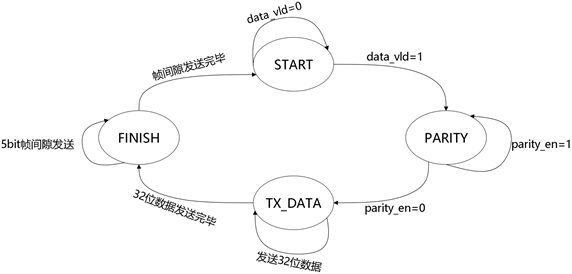

Arinc429协议的发送部分工作过程中,发送状态机是其中的核心,发送协议的状态转移图如图3所示。通过FIFO的控制读使能txfifo_rd_en有效信号和发送使能信号tx_en有效信号产生一个数据有效信号data_vld,当data_vld为1的时候,从START状态进入奇偶校验状态PARITY,奇偶校验状态会将数据的前31位进行按位异或操作,通过判断出“1”的个数,奇偶校验状态选择奇偶校验电路生成的校验位(第32位)进行输出。完成奇偶校验之后进入数据发送状态TX_DATA,数据发送状态下,32位的发送数据按照发送要求,被串行顺序发出,当dout输出为1,tx0_out和tx1_out的数据位(即前半周期)分别输出1和0;dout输出为0时,tx0_out和tx1_out的数据位分别输出0和1。通过dout_ack输出响应有效信号,判断当前32位数据是否发送完毕,发送完毕进入发送完成状态FINISH,发送完成状态通过等待5位中电平0V的时间(即5 bit时间),此时tx0_out和tx1_out均输出0,之后状态机再回到开始状态START。

Figure 3. Send state machine state transition diagram

图3. 发送状态机状态转换图

其中rate_sel为发送率,为“1”时选择12.5Kbps,为“0”时选择100Kbps;parity_en为奇偶检验使能,为“1”时表示奇校验使能,为“0”时表示不使能;tx_line_sw为端口物理交换信号,为“1”时表示选择tx0_out、tx1_out分别为高、低电平,为“0”时表示选择tx0_out、tx1_out分别为低、高电平;ifg_slot_cfg为帧间隙,发送完一帧之后,默认保持5位中电平0V的时间。ARINC429发送端逻辑设计的重要部分信号如表2所示。

Table 2. ARINC429 transmitter signal definition

表2. ARINC429发送端信号定义

2.3. ARINC429接收协议逻辑设计

接收部分输入端接入两路串行数据rx0_in、rx1_in (即TTL“1”、TTL“0”),经过源/目的地识别码校验、符号状态码识别、奇偶校验等过程,转换成32位的并行数据字,以供上位机读取。其中,接收部分由总线接口、异步FIFO设计、奇偶校验、寄存器控制、串并转换等模块组成。

接收部分主要完成数据接收、数据校验、数据写入。

数据接收工作过程:通过LBE总线控制接收使能信号rx_en,启动数据接收,且从5位字间隙判断到数据起始位,此时寄存器根据设置的位速率,开始数据接收,其中接收端采样输入端rx0_in、rx1_in信号的前半周期数据,按照rx0_in的前半周期为1、rx1_in的前半周期为0,接收端输出为1、rx0_in的前半周期为0、rx1_in的前半周期为1,接收端输出为0的要求,依次进行串行接收32位数据,接收完成后完成串并转换,得到32位并行数据rx_data[31:0]。将得到的32位并行数据重新组合,即调整rx_data[31:0]的低八位标号位数据,以此正确还原接收的数据,具体调整为rx_fifo_wdata<= {rx_data[31:8],rx_data[0],rx_data[1],rx_data[2],rx_data[3],rx_data[4],rx_data[5],rx_data[6],rx_data[7]}。

数据校验工作过程:LBE总线控制奇偶校验使能信号parity_en,第32位的数据,会根据发送端的低31位数据,判别出相应的奇偶校验位值rx_p,并与发送端的奇偶检验位tx_data_p进行比对,产生一个接收部分的奇偶校验比对信号p_bit_ind。p_bit_ind为“1”,表示比对结果一致,反之不一致;LBE总线控制源/目的识别码过滤使能信号sdi_filter_vector,将接收的ARINC429数据rx_data[9:8]与发送端对应的2位数据进行比对,产生一个SDI比对信号sdi_match,sdi_match为“1”,表示接收的2位数据与发送端的一致,反之不一致;LBE总线控制标号位过滤使能信号label_filter_en,将接收的ARINC429标号位数据与发送端对应的8位数据进行比对,产生一个label比对信号label_match。label_match为“1”,表示接收的8位数据与发送端的一致,反之不一致。

数据写入工作过程:数据校验模块产生的三个比对信号均为“1”且数据没有写满的情况下,通过设置Label过滤操作偏移地址label_filter_offset的最大偏移量,计算出正确的接收地址,完成32位并行数据的写入。其中ARINC429接收端逻辑设计的重要部分信号如表3所示。

Table 3. ARINC429 receiver signal definition

表3. ARINC429接收端信号定义

3. 硬件电路设计

3.1. 改进方案

传统的ARINC429电路是通过进口的协议芯片(如HS-3282)加驱动芯片(如HS-3182)实现 [10],如图4所示。HI-3282实现数据接收和发送 [11],HI-3182实现总线发送驱动功能 [12]。局限在于HI-3282协议芯片只有1路发送通道,2路接收通道,使得通道通信数量有限,且扩展不方便。改进的通信电路实现方案如图5所示。通过在FPGA设计ARINC协议,以此替代进口的协议芯片 [13],节省板卡面积、克服协议芯片单通道通信,特别是当需要多个ARINC429通道通信时,可灵活扩展发送通道数量。SM8444接收器芯片可同时接入4通道通信,FPGA型号采用国产芯片复旦徽FMQL45T900,驱动芯片采用国产国徽芯片(SM8444与SM0429),从而解决了ARINC429的国产化问题。

Figure 4. Traditional ARINC429 communication circuit scheme

图4. 传统型ARINC429通信电路方案

Figure 5. Multi-channel localized improved ARINC429 communication circuit scheme

图5. 多通道国产化改进型ARINC429通信电路方案

3.2. 硬件电路设计

ARINC429数据发送:将控制系统FPGA输入的串行数据分别从DATA(A)和DATA(B)引脚输入,芯片通过SYNC和CLOCK信号使能,输出电压幅度可通过VREF进行调节。典型情况下,VREF = V1 = 5 V。因此,单端输出+5 V、−5 V和0 V电压,差分输出电压为10 V。ARINC429总线发送器SM0429与FPGA硬件电路设计如图6所示。

Figure 6. ARINC429 bus transmitter and FPGA hardware design diagram

图6. ARINC429总线发送器与FPGA硬件设计图

ARINC429数据接收:SM8444是一款四通道ARINC429接收器,接收来自ARINC429总线上的信号,并转换成CMOS/TTL信号输出。通过线缆与ARINC429总线发送器相连。ARINC429总线发送器负责发送信号 [14],通过线缆传输到SM8444接收端,经过电路处理转换成CMOS/TTL信号输出并传输到FPGA [15]。ARINC429总线接收器SM08444与FPGA硬件电路设计如图7所示。

Figure 7. ARINC429 bus receiver and FPGA hardware design diagram

图7. ARINC429总线接收器与FPGA硬件设计图

4. 仿真验证

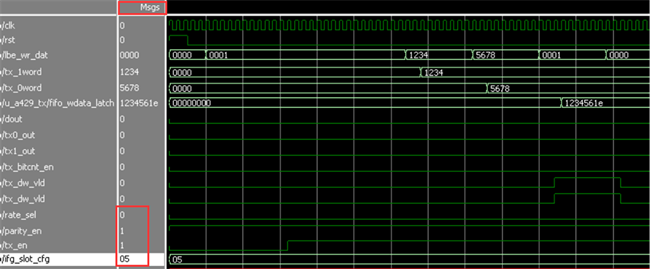

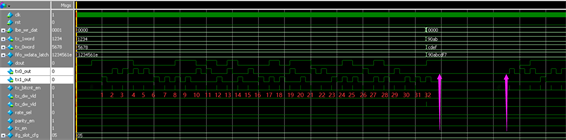

本设计是基于Vivado和questasim进行仿真验证,通过编写testbench,设置rate_sel寄存器为1'b0,选择位速率为高速100Kbps;设置parity_en寄存器为1'b1,选择奇校验使能;设置tx_en寄存器为1'b1,开启发送使能;设置ifg_slot_cfg[4:0]寄存器为默认的5'd5,选择最小帧间隙为5bit等待时间。各个寄存器设置,如发送部分数据第一次写入仿真波形图8矩形标注的Msgs一栏中的值,与testbench代码各个寄存器设置的一致。要发送的32位ARINC429数据分为2路各16位, 高16位tx1_word、低16位tx0_word分别由LBE总线协议,通过lbe总线数据写入信号lbe_wr_dat,写入第一次数据16'h1234,16'h5678;第二次写入数据16'h90ab,16'hcdef。发送部分第一次写入数据仿真波形和第二次写入数据仿真波形分别如图8及图9所示。从图8可以看到第一次向tx1_word信号输入了16'h1234,tx0_word输入了16'h5678;从图9可以看到第二次向tx1_word信号输入了16'h90ab,tx0_word输入了16'hcdef。

Figure 8. ARINC429 sends part of the first write data simulation waveform

图8. ARINC429发送部分第一次写入数据仿真波形

Figure 9. ARINC429 sends part of the second write data simulation waveform

图9. ARINC429发送部分第二次写入数据仿真波形

在向tx1_word和tx0_word写入数据之后,写入的数据需要存入FIFO中,等待开启发送使能有效信号tx_en之后,发送存入的32位数据。而需要注意,发送数据需要遵循以下传输协议:先发送第1位,然后依次发送至32位,先传标号位,后传数据。当传输数据时,先传输最低位,但标号位应先传最高位,后传最低位。所以存入FIFO的32位数据fifo_wdata_latch[31:0]需要按照传输的发送协议,对8位标号位数据tx_0word[7:0]进行调整,即fifo_wdata_latch<={tx_1word[15:0],tx_0word[15:8],tx_0word[0],tx_0word[1],tx_0word[2],tx_0word[3],tx_0word[4],tx_0word[5],tx_0word[6],tx_0word[7]},这样才能保证按照发送协议进行正确传输32位数据。从图8可以看到第一次存入FIFO的32位数据fifo_wdata_latch[31:0]为32'h1234561e,转为二进制格式为32'b32'b0001_0010_0011_0100_0101_0110_0001_1110,将tx_1word[15:0]的16'h1234转为二进制格式为16'b0001_0010_0011_0100,tx_0word[15:0]的16'h5678转为二进制格式数据为16'b0101_0110_0111_1000。将fifo_wdata_latch与tx_1word和tx_0word的二进制格式数据对比分析,可以看到,fifo_wdata_latch[31:0]数据的低八位为8'b0001_1110,这8位是标号位数据,是将tx_0word[15:0]低八位的数据8'b0111_1000进行高低位转换得到,这样既满足了先传标号位的要求,又满足了标号位先传最高位,后传最低位的要求。

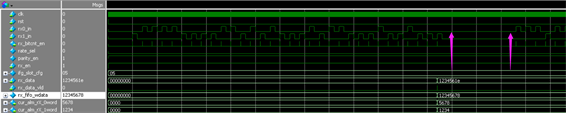

发送第一次和第二次写入的数据如图10和图11所示,从图10可以看到单bit数据输出信号dout的波形图,从波形的电平起始可以分析出,在系统时钟clk下,依次是0111_1000_0110_1010_0010_0011_0100_1000,共32位数据。正是按照fifo_wdata_latch[31:0]数据32'h1234561e的二进制格式:32'b0001_0010_0011_0100_0101_0110_0001_1110,按照先传输低位要求,依次串行输出fifo_wdata_latch的32位数据,而两路TTL电平差分输出信号tx0_out和tx1_out则是严格按照单bit数据输出信号dout进行转换输出,dout串行输出的第1位为0,此时在图10标注的数字1后面,tx0_out输出前半个周期为0,后半个周期为0,tx1_out输出前半个周期为1,后半个周期为0。dout串行输出的第2位为1,此时在图10标注的数字2后面,tx0_out输出前半个周期为1,后半个周期为0,tx1_out输出前半个周期为0,后半个周期为0。两路TTL电平差分输出信号按照前半个周期输出数据,后半个周期输出同时为0要求,依次串行输出。至dout串行输出的32位为0,此时在图10标注的数字32后面,tx0_out输出前半个周期为0,后半个周期为0,tx1_out输出前半个周期为1,后半个周期为0,同时此刻发送数据完成有效信号tx_dw_vld产生一个高电平,代表32位数据发送完成。至此输入的32位数据发送完毕,两路TTL电平差分输出信号tx0_out和tx1_out输出与预期波形一致,数据发送成功。在数据发送完毕之后,tx0_out和tx1_out均输出为0,即通过保持5位中电平0 V的时间(即5 bit时间),保持时间如图10标记的两个紫色箭头。之后两路TTL电平差分输出信号tx0_out和tx1_out再发送第二次写入的数据fifo_wdata_latch[31:0]为32'h90abcdf7,第二次数据发送仿真波形如图11所示,可以看到tx0_out和tx1_out输出与预期波形一致,数据发送成功。

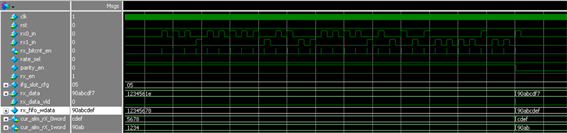

在Vivado平台,将设计好的发送协议与接收协议搭建回环测试并编写testbench,将ARINC429总线发送的串行数据接入接收协议的输入端rx0_in、rx1_in,如上设置位速率为高速100Kbps、奇校验使能、接收使能、最小帧间隙5 bit。在接收使能信号rx_en开启之后,接收端采样输入端rx0_in、rx1_in的前半周期数据,按照rx0_in的前半周期为1、rx1_in的前半周期为0,接收端输出为1、rx0_in的前半周期为0、rx1_in的前半周期为1,接收端输出为0的要求,依次串行接收并经过串并转换后,将得到的数据重新组合,即调整rx_data[31:0]的低八位,以此正确还原接收的数据,具体调整为rx_fifo_wdata<= {rx_data[31:8],rx_data[0],rx_data[1],rx_data[2],rx_data[3],rx_data[4],rx_data[5],rx_data[6],rx_data[7]},第一次接收处理后得到32位并行数据rx_fifo_wdata为32'h12345678,分别为高16位cur_alm_rx_1word数据16'h1234,低16位cur_alm_rx_0word数据16'h5678。第一次接收部分的仿真波形如图12所示(部分截图),与第一次发送的数据一致,数据接收成功。在接收完第一次发送的数据之后,rx0_in、rx1_in均保持为0,即通过保持5位中电平0 V的时间(即5 bit时间),保持时间如图12标记的两个紫色箭头。之后两路TTL电平差分输入信号rx0_in、rx1_in再接收第二次发送的数据。第二次数据发送仿真波形如图13所示,可以看到第二次接收处理后得到32位并行数据rx_fifo_wdata为32'h90abcdef,分别为高16位cur_alm_rx_1word数据16'h90ab,低16位cur_alm_rx_0word数据16'hcdef,与第二次发送的数据一致,数据接收成功。

Figure 10. ARINC429 first data transmission simulation waveform

图10. ARINC429第一次数据发送仿真波形

Figure 11. ARINC429 second data transmission simulation waveform

图11. ARINC429第二次数据发送仿真波形

Figure 12. ARINC429 first data receiving simulation waveform

图12. ARINC429第一次数据接收仿真波形

Figure 13. ARINC429 second data receiving simulation waveform

图13. ARINC429第二次数据接收仿真波形

5. 结论

本文ARINC429总线协议的设计基于Verilog HDL语言,FPGA型号使用了复旦徽国产的FMQL45T900、ARINC驱动器采用国徽国产芯片SM8444与SM0429。通过仿真验证,结果表明ARINC429总线协议能够实现多通道数据的收发,设计符合ARINC429总线数据传输要求,该电路可应用于各种使用ARINC429总线的场合。

综上所述,基于国产FPGA设计的多通道ARINC429总线有如下特点:

1) 无需依赖进口的ARINC429协议芯片和驱动芯片,可同时实现4路发送、4路接收的多通道通信,总线数据支持高速和低速多种工作方式,真正实现广泛应用的目的。

2) 不依赖Xilinx自身IP核FIFO,基于Verilog HDL语言自写FIFO缓存器,充分利用时钟同步打拍方法,提高了可靠性,有效解决了数据间干扰和亚稳态问题 [16],完全可以保证传输过程中数据字之间为5位字间隔。

3) 基于FPGA的ARINC429协议的设计,极大地方便了硬件工程师设计PCB电路,节省了板卡面积,方便通信通道的扩展,有效地提升了数据通信模块的处理能力和集成度,降低了研发成本,提高了研发效率。

基金项目

西南民族大学中央高校基本科研业务费专项资金项目+2021NYYXS82。

NOTES

*通讯作者。