1. 引言

接触窗(Contact window)是前后端工艺的连接通道(图1),受填孔能力的限制,接触窗中的TiN从0.18 μm开始采用金属有机物化学气相沉积MOCVD (Metal-Organic Chemical vapor Deposition)工艺 [1] [2]。MOCVD工艺由TDMAT (四次二甲基铵基钛)在一定的温度和压力下分解后先沉积TiN薄膜,再利用Plasma treatment,减低薄膜中的碳,氢杂质,最后得到低阻、致密的TiN薄膜。沉积和Plasma treatment是套循环步骤。为了将杂质去除的更加彻底,芯片制造中一般进行多次循环,每个循环沉积的薄膜厚度尽可能薄一些。

RC Delay会严重影响芯片的性能,为了控制RC值,MOCVD工艺对成膜均一性和厚度有严格的要求。MOCVD工艺对温度极其敏感,尤其是腔体Kits PM后,因为腔体Condition变化大,需要通过多次工艺参数调机,才能满足工艺的膜厚和均一性要求,严重影响了机台的Uptime。本文从MOCVD腔体气流方向和Kits PM过程中更换的部件出发,分析影响MOCVD工艺成膜厚度和均一性的可能因素,通过在PM过程中提前干预,降低Kits PM后的调机率,提高机台Uptime。未做任何干预的PM后的RS map (图2),靠近Pump port的上半圈RS值明显偏高,导致成膜均一性不符合工艺规格要求,需要通过调机来满足工艺要求。

2. 原因分析

MOCVD工艺时:Wafer坐落在腔体中心位置的Heater上,TDMAT经过LFM流量控制和Injector气化后,由Carrier gas带入工艺腔体顶部,再通过顶部Shower head均匀分散地流到工艺腔体里的Wafer上参与反应 [3]。因TiN成膜的速度和温度成正相关,为了保证成膜的均一性,Wafer的背面在沉积薄膜的步骤会通入Backside gas,使Wafer受热更加均匀,wafer的四周边缘底部会有Purge gas,防止Wafer bevel发生薄膜沉积。所有多余的反应气体途径左侧Pumping port,经过Rough Valve由Pump抽走(图3)。

Figure 3. MOCVD chamber structure diagram

图3. MOCVD腔体结构示意图

Heater的四周由Outer Shield,inner shield,Chamber Insert环绕,防止Chamber body发生薄膜沉积。Kits PM时,每次都需要更换用于分散气流的Shower head和用于保护Chamber body的Outer shield,inner shield及Chamber insert。

由MOCVD工艺的气流方向及Kits PM更换的部件可以推测 [4] [5]:

1) 靠近Pumping port 抽力大,气流运动快导致该区域Wafer温度偏低,造成上半圈成膜偏薄;

2) 用于保护Chamber body的Kits,其表面的Condition会影响腔体内部的热环境,对成膜的厚度影响较大;

3) 用于分散工艺反应气体的Shower head的孔径大小可以直接影响每个区域参与反应的气体量,对成膜均一性有密切的相关性。

3. 验证实验

3.1. 实验方案

针对上述的三个推测,设计3个对应的实验改善方案:

方案1:将腔体的handoff中心值−80 Step,提升靠近Pumping port区域Wafer的实际温度。Wafer坐落在Heater上作业时,为了防止wafer bevel沉积薄膜,会在wafer Edge位置流Purge gas。Wafer上接触到Edge Purge gas的区域Wafer温度相对较低。实验中通过将Robot的handoff Extension方向减少80 step,将Wafer整体远离Pumping port 0.5 mm左右,使原本靠近Pumping Port端的Wafer被Edge purge gas影响到的区域变小,提升wafer的温度。

方案2:根据每套Kits在每个腔体最近一次测机合格的C0为标准值,在PM过程中进行预调。C0是Heater温度的Offset补偿值,每套Recycle Kits的Condition都会有一定的差异,安装到腔体后,Kits的吸热量会有一定的差异,最终造成Wafer上的温度出现一定的偏差。通过调整C0来调节MOCVD工艺腔体内Heater的实际温度,从而调整Wafer的工艺温度。

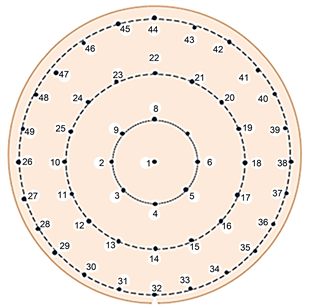

方案3:对Shower head孔洞直径进行管控,确保工艺时工艺气体均匀分散到Wafer表面。成膜均一性由Monitor Wafer量测49个点RS值计算得到,量测点坐标以环型分部(图4)。实验中通过将Shower head上被采样用于量测的孔洞位置也设置为环形分部,管控Shower head上5圈管控孔洞直径均值的差值最大值 < 30 μm,以保证工艺气体尽可能的分布均匀。

Figure 4. Section diagram of RS measurement points

图4. RS量测点分部图

3.2. 实验设备

3个验证实验全部在上海华力微电子有限公司FAB内的AMILBA01和AMILBA02两台量产机台上的4个TxZ腔体上进行开展(图5)。

Figure 5. Appearance picture of TxZ chamber

图5. TxZ腔体外观图

3.3. 实验结果与分析

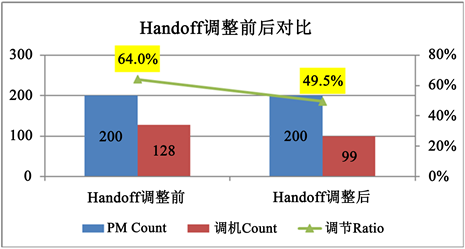

实验1:依据4个腔体的中心值Handoff,Extension 方向分别减少80 Step作为实验设定值(表1),观察200个PM,统计整体的调机率。

Table 1. Chamber handoff value setting

表1. 腔体handoff值设定

实现结果显示,200个PM中需要通过调机的个数由原先的128个降低到99个。通过Wafer handoff的预调,Kits PM后的调机率由handoff预调前的64%降低到49.5% (图6)。

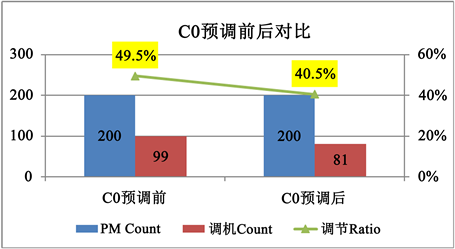

实验2:记录每套Kits在4个腔体测机合格的C0值(记录表格式见表2),在下次该Kits安装到对应腔体时,依据上一次记录的值作为标准值,在PM过程中进行预调,依据此方式观察200个PM,统计整体的调机率。

实验结果显示,200个PM中需要通过调机的个数由原先的99个进一步降低到81个。通过预调C0,Kits PM后的调机率由49.5%进一步降低到40.5% (图7)。

Figure 6. The adjustment rate after presetting of Handoff

图6. 预调Handoff后的调机率

Figure 7. The adjustment rate after presetting of C0

图7. 预调C0后的调机率

实验3:管控Shower head上5圈管控孔洞直径均值的差值最大值 < 30 μm (管控表格式见表3),依据此方式观察200个PM,统计整体的调机率。

实验结果显示,200个PM中需要通过调机的个数由原先的81个进一步降低到64个。通过对Shower head孔洞直径的管控,Kits PM后调机率由40.5%进一步降低32% (图8)。

Figure 8. The adjustment rate after the control of the aperture size of Shower Head

图8. 管控Shower Head孔径尺寸后的调机率

4. 结论

综上所述,MOCVD的成膜厚度和成膜均一性因受温度和工艺气体分布影响较大,导致PM后调机率很高,对机台的Uptime影响较大。通过对handoff的管控,实现Wafer温度偏低区域的温度提升;通过By Kits和By腔体的C0管控,实现Wafer实际成膜温度的有效控制;通过管控Shower head每圈孔径直径均值的最大差值 < 30 μm,实现对工艺气体分布的有效管控;以上三种方法同时使用,MOCVD工艺腔体PM后的调机率由64%降低到了32%,有效地提高了设备Uptime。

致谢

MOCVD工艺腔体是接触窗成膜工艺设备的瓶颈腔体,通过降低MOCVD工艺腔体PM后的调机率,可有效提升设备的Uptime。感谢设备工程师张啸,黄磊在问题讨论和实验设计阶段的合理建议,感谢工艺工程师蔡俊晟帮忙提供RS Monitor Wafer量测坐标数据,感谢制造部同事帮忙安排机台时间用于开展实验数据的收集。

参考文献