1. 引言

随着芯片集成度越来越高,随机存储器(random access memory, RAM)在片上系统(system on chip, SoC)中的占比也越来越高,因此RAM对SoC的面积及功耗的贡献也越来越大。相同容量的伪双口RAM (two ports RAM, TP RAM)与单口RAM (single port RAM, SP RAM)相比,前者的面积及功耗更大。降低SoC的面积及功耗可以节省成本,延长芯片寿命并进一步提升市场竞争力 [1] [2] 。而TP RAM作为RAM的一种常用类型,在SoC中的比重也很大。因此降低TP RAM的面积及功耗,是降低整个SoC面积及功耗的有效途径。

文献 [3] 提出一款可以工作在极低电源电压条件下,功耗较低的亚阈值SRAM存储单元。为使其设计在极低电源电压条件下依然能够保持足够的鲁棒性,采用差分读出方式和可配置的操作模式。为了降低电路功耗,采用自适应泄漏电流切断机制,可降低动态操作和静态操作时的泄漏电流。文献 [4] 提出一种适用于自旋磁随机存储器的低压写入电路,利用列选和读写隔离相结合的方法,减小写入支路上的电阻,从而降低写入功耗,并可提高自旋转移力矩磁随机存储器的存储可靠性。文献 [3] [4] 中方法都是从RAM存储单元的内部结构进行设计和优化,需要改变RAM模块自身设计。而文中介绍的方法是将TP RAM作为一个整体替换成SP RAM,替换后的RAM可以作为IP直接使用。

为了降低TP RAM的面积及功耗,本文提出一种TP RAM的优化设计方法。在TP RAM读写时钟相同的情况下,将TP RAM替换成SP RAM,并在SP RAM外围增加读写接口转换逻辑,优化后的RAM对外接口不变,并可实现原TP RAM的功能。为了进一步降低功耗,使用自适应门控时钟,对地址总线进行格雷编码。该优化方法可使RAM面积减少24.76%,功耗降低44.89%。

2. TP RAM的低功耗设计

2.1. TP RAM替换成SP RAM的必要性

SP RAM只有一套地址总线和数据总线,读写不能同时进行。TP RAM指伪双口RAM,有两套地址总线,一套数据总线,一个口只能写,另一个口只能读。RAM的功耗组成包括动态功耗及静态功耗,总功耗等于二者之和。动态功耗大小与逻辑面积,频率及逻辑翻转率成正比。在TP RAM读写时钟相同的情况下,将TP RAM替换成2倍频率的SP RAM来实现原TP RAM的功能。由于频率变成优化前的2倍,原TP RAM的一个周期时间等于优化后的SP RAM的2个周期时间,因此SP RAM逻辑翻转率将降低为原来的一半。而相同容量的SP RAM的逻辑面积比TP RAM的小,所以优化后的SP RAM的动态功耗比TP RAM的小 [5] [6] 。静态功耗大小与逻辑面积成正比,由于相同容量的SP RAM的逻辑面积比TP RAM的小,所以优化后的SP RAM的静态功耗会变小。由于替换成SP RAM需要增加的接口控制逻辑很少,与RAM本身的逻辑面积相比基本可以忽略,因此优化后的SP RAM总功耗及面积均会减小。

2.2. 读写接口转换

项目中需要使用很多读写时钟相同的先进先出存储器(first in first out, FIFO),优化前这些FIFO的RAM都使用了TP RAM,运行频率都是325 MHz。使用TSMC的28 nm HPC的Memory compiler也可以生成相同容量的频率为650 M的SP RAM。将这些TP RAM替换成SP RAM后就可以达到减少面积及降低功耗的目的。为了使替换后的SP RAM实现原TP RAM的功能,需要在SP RAM外围增加TP2SP转换逻辑。将TP RAM转换成SP RAM的转换逻辑框图如图1所示。从图1可以看到,325 M时钟域的读写控制信号经过TP2SP转换逻辑后变成了650 M时钟域的SP RAM的读写控制信号,同时SP RAM的读出数据需要转换成325 M时钟域的读出数据,且替换后的TP2SP RAM的对外接口和原TP RAM的一致。表1列出了图1中各个信号的含义,其中有外部接口信号,也有内部接口信号,内部接口信号是直接与替换后的SP RAM连接的信号。

Figure 1. Diagram of TP2SP RAM interface

图1. TP2SP RAM转换逻辑框图

Table 1. Interface signals of TP2SP RAM conversion logics

表1. TP2SP RAM转换逻辑框图接口信号列表

2.3. 低功耗方法详细设计

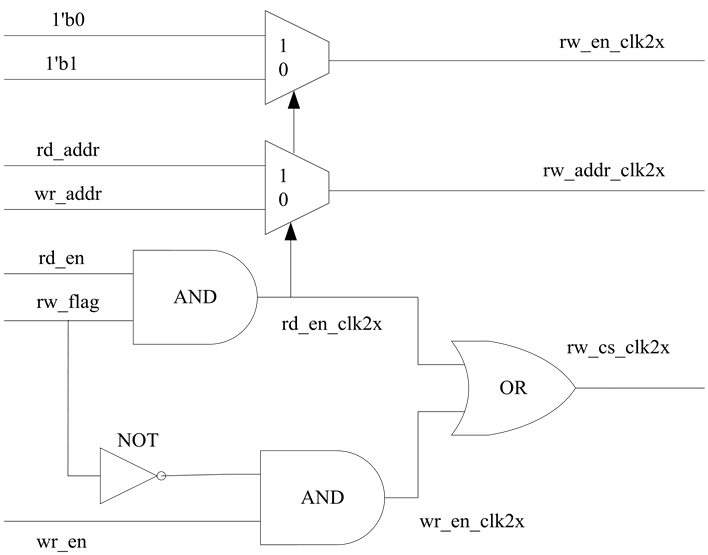

SP RAM只有一组读写控制信号,TP RAM有两组读写控制信号,所以需要将TP RAM的两组读写控制信号转换成SP RAM的一组读写控制信号。clkx是325 M的TP RAM的时钟信号,clk2x是650 M的SP RAM的时钟信号,由于TP RAM可能存在读写冲突,而SP RAM不会有读写冲突,因此读写转换逻辑需要支持TP RAM的两种场景:(1) 读写冲突时,读出新数据,写入新数据,即先写后读;(2) 读写冲突时,读出旧数据,写入新数据,即先读后写。为了控制读写冲突,需要产生一个中间信号rw_flag,逻辑生成电路如图2。先写后读的控制方法是在rw_flag = 0时写,rw_flag = 1时读;如果需要支持先读后写,则控制方法是在rw_flag = 0时读,rw_flag = 1时写。图3列出了先写后读的控制方法的相应信号

Figure 2. rw_flag generation logic

图2. rw_flag 控制信号产生逻辑

Figure 3. TP2SP diagram of first writing and after reading

图3. TP2SP先写后读控制逻辑生成示意图

生成电路,rw_en_clk2x是SP RAM的读写控制信号,当rw_en_clk2x=1时写,当rw_en_clk2x = 0时读。rw_cs_clk2x是SP RAM的片选控制信号,当rw_cs_clk2x = 1时有效。rw_addr_clk2x是SP RAM的读写地址信号。

图4所示为SP RAM读出的数据转换成保持一个TP RAM时钟周期数据的时序图,clkx是325 M的TP RAM的时钟信号,clk2x是650 M的SP RAM的时钟。rd_en是外部输入的325 M时钟域的读控制信号,rd_data_clk2x_1ff是SP RAM的输出数据rd_data_clk2x延迟一个clk2x后的数据,最终输出是能够保持一个clkx时钟周期的rd_data_clkx数据。

2.4. 格雷码优化

格雷码是二进制编码的变形,任意两个相邻整数的编码只有一位差异。普通二进制码与格雷码可以按以下方法进行转换:二进制码转换成格雷码(编码):从最左位起,依次将每一位与右边一位进行异或运算,作为对应格雷码该位的值,最左边一位不变;格雷码转换成二进制码(解码):从左边第二位起,将每位与左边一位解码后的值进行异或运算,作为该位解码后的值,最左边一位依然不变。由于任意两个相邻地址编码之间转换只有一位发生变化,大大减少了地址总线的翻转次数,从而可降低芯片的动态功耗 [6] [7] 。自适应门控时钟及格雷码转换模块的面积较小,与RAM本身的逻辑面积相比基本可以忽略。

2.5. 动态电压调整技术及合理的电源分区策略

电路可以正常工作的最高频率只和电压、温度有关,故可以在芯片内部使用cell延迟、然后通过与非门产生时钟,因为电压已知,所以可以通过该时钟的频率间接知道温度;知道温度、电压,则可以知道CPU所能跑的最高频率。具体操作的时候,可进行一次高低温试验,将不同电压、温度下,环路时钟频率和CPU所能跑的最高时钟进行测量,这样根据环路时钟频率,电压,得知温度,然后查出CPU所能运行的最高频率。这样设计时只要留一定的余量就可以配置CPU频率。CPU配置新电压流程:1、升压的时候,加较多电压余量,争取一次电压调整能到CPU要求的频率,然后进行循环,逐渐降低电压。

Figure 4. Timing diagram of conversion logic for output data

图4. 输出数据转换时序图

2、减压的时候,1/2法逐步降低。在划分电源分区时,需要考虑一个电源区里的模块是否具有“工作时段基本同步”的特性,尽量将在同一时段工作及不工作的模块放在一个电源分区里。电源分区的数量设计要结合实际项目进行综合考虑,过多的电源分区会增加实现复杂度及芯片面积,过少的电源分区不利于降低静态功耗。电源分区确定之后,当某个电源区里的所有模块都不需要工作时,可以将这个电源区的工作电压关闭从而将该模块的静态功耗降为0。如果由于某些原因而无法完全关闭某个电源区的工作电压,采取降低工作电压的方式也可以减少这个电源区的静态功耗 [8] 。

3. 低功耗设计方法在芯片中的应用

优化前的TP RAM包括2种长宽类型,一种是768 × 49,另一种是320 × 64。使用本文的优化方法将所有TP RAM替换成倍频的SP RAM。表2及表3列出了芯片中使用的TP RAM及优化后的SP RAM的规格及相应面积和功耗数据。其中功耗是指动态功耗与静态功耗之和,由于动态功耗大小与读写翻转率成正比 [9] [10] ,所以表中也列出了相应的读写翻转率数据。由于优化后TP RAM变成了频率翻倍的SP RAM,所以读写翻转率均变成优化前的一半。表中TP指TP RAM,SP指SP RAM;Compiler Lib是指生成memory时的compiler library类型,rf-2p-uhde是指register file two port ultra-high density;由于功耗还与温度及电压有关,所以表中也列出了工艺Corner:TT/0.9V/85C。数量是指这种memory在芯片中使用的个数,768 × 49的memory使用了750个,320 × 64的memory使用了510个。

4. 仿真结果及分析

优化前所有的TP RAM和SP RAM的面积总和为31.75 mm2,功耗为0.548 W;优化后的面积总和为23.89 mm2,功耗为0.302 W。优化后memory面积减少24.76%,功耗减少44.89%。表4列出了优化前后芯片memory面积及功耗对比数据。为了测试memory的功耗,每个memory都设计成具有旁路功能,当开启某memory旁路功能后,该memory的输入直接穿透到输出,此时测试的芯片功耗中该memory的功

Table 2. Data comparison between TP RAM and SP RAM in size 768 × 49

表2. 768 × 49的TP RAM与SP RAM对比

Table 3. Data comparison between TP RAM and SP RAM in size 320 × 64

表3. 320 × 64的TP RAM与SP RAM对比

Table 4. Area and power comparison between before optimization and after

表4. 优化前后芯片memory面积及功耗对比列表

耗为0;当关闭该memory旁路功能后测试的芯片功耗就包含了该memory的功耗。该memory旁路前后测试的芯片功耗之差就等于该memory的功耗 [11] 。

优化后的芯片经TSMC 28 nm HPC工艺实现,封装类型是FCBGA33*33,使用了8个ARM Cortex-A15核,CPU运行最高频率为1.3 GHz。

5. 小结

本文通过将读写时钟相同的TP RAM替换成倍频的SP RAM,并在SP RAM外围增加读写接口转换逻辑,使替换后的RAM实现原TP RAM的功能,从而达到降低功耗的目的。为了进一步降低功耗,对地址总线进行格雷编码,采用动态电压调整技术及合理的电源分区策略。仿真结果表明:优化后的RAM面积减少了24.76%,功耗降低了44.89%。